|

9.3.1 通用I/O(GPIO) 在复位期间及复位刚刚完成后,复用功能尚未激活,大多数 I/O 端口被配置为输入浮空模式。 复位后,调试引脚处于复用功能上拉/下拉状态: • PA15:JTDI 处于上拉状态 • PA14:JTCK/SWCLK 处于下拉状态 • PA13:JTMS/SWDAT处于上拉状态 • PB4:NJTRST 处于上拉状态 • PB3:JTDO 处于浮空状态 当引脚配置为输出后,写入到输出数据寄存器 (GPIOx_ODR) 的值将在 I/O 引脚上输出。可以在推挽模式下或开漏模式下使用输出驱动器(仅驱动低电平,高电平为高阻态)。 输入数据寄存器 (GPIOx_IDR) 每隔 1 个 AHB 时钟周期捕获一次 I/O 引脚的数据。 所有 GPIO引脚都具有内部弱上拉及下拉电阻,可根据 GPIOx_PUPDR 寄存器中的值来打开/关闭。

9.3.2 I/O 引脚复用功能复用器和映射 器件 I/O引脚通过一个复用器连接到板载外设/模块,该复用器一次仅允许一个外设的复用功能 (AF) 连接到 I/O 引脚。这可以确保共用同一个 I/O 引脚的外设之间不会发生冲突。 每个 I/O 引脚都有一个复用器,该复用器采用多达 16 路复用功能输入(AF0 到 AF15),可通过 GPIOx_AFRL(针对引脚 0 到 7)和 GPIOx_AFRH(针对引脚 8 到 15)寄存器对这些输入进行配置: • 复位后,复用器选择为复用功能 0 (AF0)。在复用模式下通过 GPIOx_MODER 寄存器配置 I/O。 • 器件数据手册中详细说明了每个引脚的特定复用功能分配。 除了这种灵活的 I/O 复用架构之外,各外设还可以将复用功能映射到不同 I/O 引脚,这可以优化小型封装中可用外设的数量。

要将 I/O 配制成所需功能,必须按照以下步骤操作: • 调试功能:每个器件复位后,立即将这些引脚分配为可由调试主机使用的复用功能引脚。 • GPIO:在 GPIOx_MODER 寄存器中将所需 I/O 配置为输出、输入或模拟通道。 • 外设复用功能: – 在 GPIOx_AFRL 或 GPIOx_AFRH 寄存器中,将 I/O 连接到所需的 AFx。 – 通过 GPIOx_OTYPER、GPIOx_PUPDR 和 GPIOx_OSPEEDER 寄存器,分别选择类型、上拉/下拉以及输出速度。 – 在 GPIOx_MODER 寄存器中将所需 I/O 配置为复用功能。 • 其它功能: – 对于 ADC、DAC、OPAMP 和 COMP,在 GPIOx_MODER 寄存器中将所需 I/O 配置为模拟模式,并在 ADC 、DAC、OPAMP和 COMP 寄存器中配置所需功能。对于ADC,需要配置GPIOx_ASCR 寄存器。 – 对于 RTC、WKUPx 和振荡器的其它功能,在相关的 RTC、PWR 和 RCC 寄存器中配置所需功能。这些功能优先于标准 GPIO 寄存器中的配置。 有关复用功能 I/O 引脚映射的详细信息,请参见器件数据手册中的“复用功能映射”表。

9.3.3 I/O 端口数据寄存器 每个GPIO端口有4个32位存储器映射的控制寄存器(GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR、GPIOx_PUPDR),可配置多达16个 I/O。GPIOx_MODER 寄存器用于选择 I/O 模式(输入、输出、AF、模拟)。GPIOx_OTYPER 和 GPIOx_OSPEEDR 寄存器用于选择输出类型(推挽或开漏)和速度。无论采用哪种 I/O 方向,GPIOx_PUPDR 寄存器都用于选择上拉/下拉。

9.3.4 I/O 端口数据寄存器 每个 GPIO 都具有 2 个 16 位数据寄存器:输入和输出数据寄存器(GPIOx_IDR 和GPIOx_ODR)。GPIOx_ODR 用于存储待输出数据,可对其进行读/写访问。通过 I/O 输入的数据存储到输入数据寄存器 (GPIOx_IDR) 中,它是一个只读寄存器。 有关寄存器说明的详细信息,请参见第 9.4.5节:GPIO 端口输入数据寄存器 (GPIOx_IDR)(x = A..K)和第9.4.6节:GPIO端口输出数据寄存器 (GPIOx_ODR) (x = A..K)。

9.3.5 I/O 数据位操作 置位复位寄存器 (GPIOx_BSRR) 是一个 32 位寄存器,它允许应用程序在输出数据寄存器(GPIOx_ODR) 中对各个单独的数据位执行置位和复位操作。置位复位寄存器的大小是GPIOx_ODR 的二倍。 GPIOx_ODR 中的每个数据位对应于 GPIOx_BSRR 中的两个控制位:BS(i) 和 BR(i)。当BS(i) 位写入 1 时,其会置位对应的 ODR(i) 位。当BR(i) 位写入 1 时,其会复位 ODR(i) 对应的位。 在 GPIOx_BSRR 中向任何位写入 0 都不会对 GPIOx_ODR 中的对应位产生任何影响。如果在 GPIOx_BSRR 中同时尝试对某个位执行置位和复位操作,则置位操作优先。 使用 GPIOx_BSRR 寄存器更改 GPIOx_ODR 中各个位的值是一个“单次”操作,不会锁定GPIOx_ODR 位。随时都可以直接访问 GPIOx_ODR 位。GPIOx_BSRR 寄存器提供了一种执行原子按位处理的方法。 在对 GPIOx_ODR 进行位操作时,软件无需禁止中断:在一次原子 AHB 写访问中,可以修改一个或多个位。

9.3.6 GPIO锁定机制 通过将特定的写序列应用到GPIOx_LCKR寄存器,可以冻结GPIO控制寄存器。冻结的寄存器包括GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR、GPIOx_PUPDR、GPIOx_AFRL和GPIOx_AFRH。 要对GPIOx_LCKR寄存器执行写操作,必须应用特定的写/读序列。当正确的LOCK序列应用到此寄存器的第16位后,会使用LCKR[15:0]的值来锁定I/O的配置(在写序列期间,LCKR[15:0] 的值必须相同)。将LOCK序列应用到某个端口位后,在执行下一次MCU复位或外设复位之前,将无法对该端口位的值进行修改。每个GPIOx_LCKR位都会冻结控制寄存器(GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR、GPIOx_PUPDR、GPIOx_AFRL 和 GPIOx_AFRH)中的对应位。 LOCK 序列(参见第 9.4.8节:GPIO端口配置锁定寄存器 (GPIOx_LCKR) (x = A..K))只能通过对GPIOx_LCKR寄存器进行字(32位长)访问的方式来执行,因为 GPIOx_LCKR 的第16位必须与 [15:0]位同时置位。 有关详细信息,请参见第 9.4.8节:GPIO 端口配置锁定寄存器 (GPIOx_LCKR) (x = A..K) 中的 LCKR 寄存器说明。

9.3.7 I/O复用功能输入/输出 有两个寄存器可用来从每个I/O可用的复用功能输入/输出中进行选择。借助这些寄存器,可根据应用程序的要求将某个复用功能连接到其它某个引脚。 这意味着可使用GPIOx_AFRL和GPIOx_AFRH复用功能寄存器在每个GPIO上复用多个可用的外设功能。这样一来,应用程序可为每个I/O选择任何一个可用功能。由于AF选择信号由复用功能输入和复用功能输出共用,所以只需为指定I/O的复用功能输入/输出选择一个通道即可。 要了解在每个GPIO引脚上复用了哪些功能,请参见器件数据手册。

9.3.8 外部中断线/唤醒线 所有端口都具有外部中断功能。要使用外部中断线,必须将端口配置为输入模式。请参见第11节:外部中断和事件控制器(EXTI)和第11.3节:唤醒事件管理。

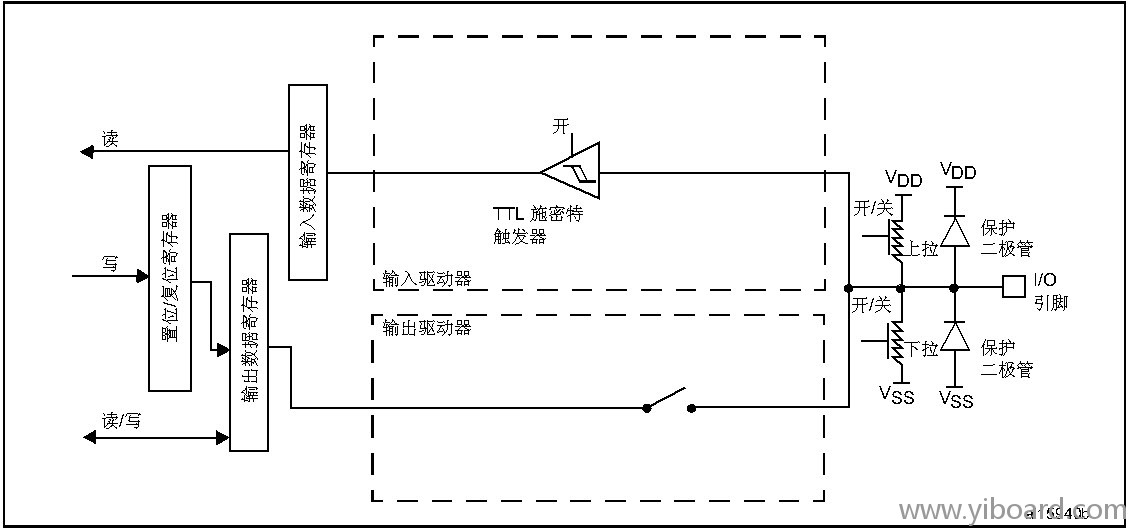

9.3.9 输入配置 对I/O端口作为输入进行编程时: • 输出缓冲器被禁止 • 施密特触发器输入被打开 • 根据GPIOx_PUPDR寄存器中的值决定是否打开上拉和下拉电阻 • 输入数据寄存器每隔1个AHB时钟周期对I/O引脚上的数据进行一次采样 • 对输入数据寄存器的读访问可获取I/O状态 图20说明了I/O端口位的输入配置。 图20. 输入浮空/上拉/下拉配置

|  |手机版|YiBoard一板网

( 冀ICP备18020117号 )

|手机版|YiBoard一板网

( 冀ICP备18020117号 )